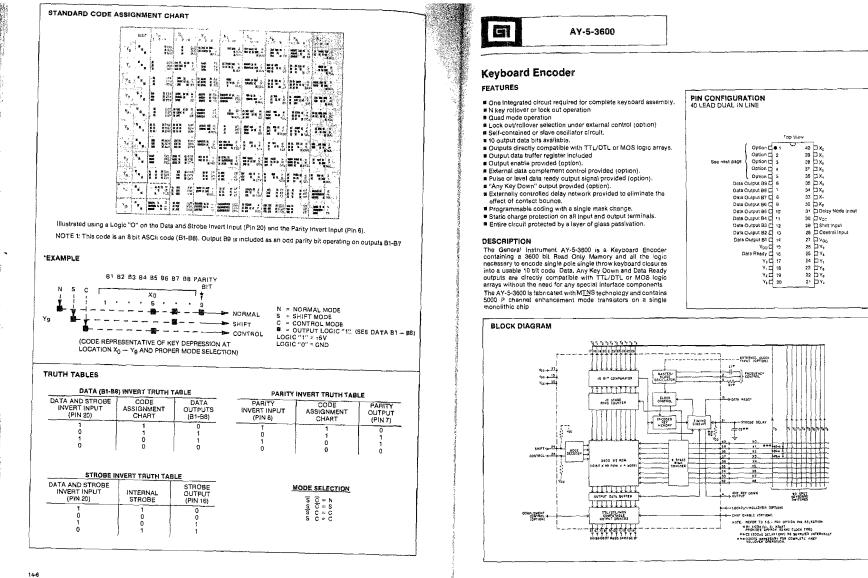

## COSTOM CODING INFORMATION

The custom coding information for General Instrument's AY-5-Resource and the second state of the second st pattern requires 92 cards (1 title card, 1 circuit option card and 90 ROM pattern cards). (See Note 1)

If it is not possible to supply punched cards, then the Truth Table should be completed (See Note 1). However, there would be a

#### PIN OPTIONS

Pins 6-40 of the AY-5-3600 are permanently assigned. The functions assigned to ping 1-5 depend on which functional options are selected from the following:

#### External Clock

-requires one package pin to input an external clock source. Internal Oscillator

-requires three package pins interconnected with an external RC network to develop the clock required.

Lockout/Rollover (LO/RO)

-requires one package pin to externally select N-Key Lockout or N-Key Rollover, LO = +5V, RO = GND.

Complement Control (CC)

-requires one package pin to externally control the logic state of the data bits (B1-B10) and, if required, the Data Ready output.

The following chart lists the pin assignments according to the functions selected above;

| PIN 1                                                                                  | PIN 2                                  | PIN 3                            | PIN 4                                                       |                                                   |

|----------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|-------------------------------------------------------------|---------------------------------------------------|

| External Clock<br>External Clock<br>External Clock<br>External Clock<br>External Clock | LO/RO<br>LO/RO<br>LO/RO<br>LO/RO<br>CC | CC<br>CC<br>CC<br>CE<br>CE<br>CE | СЕ<br>СЕ<br>АКО<br>АКО<br>АКО                               | AKO<br>BIO<br>BIO<br>BIO<br>BIO<br>BIO            |

|                                                                                        | Internei Oscillator                    |                                  | LO/RO<br>LO/RO<br>LO/RO<br>CC<br>CC<br>CC<br>CC<br>CC<br>CC | CC<br>CE<br>AKO<br>BIO<br>CE<br>AKO<br>BIO<br>AKO |

|                                                                                        |                                        |                                  | CE<br>CE<br>AKO                                             |                                                   |

# ELECTRICAL CHARACTERISTICS

# Maximum Ratings\*

$V_{\rm DD}$  and  $V_{\rm GD}$  (with respect to  $V_{\rm CC})$ Logic Input voltages (with respect to Vcc) -20V to +0.3V Storage Temperature -65°C to +150°C - 55°C to +150°C Operating Temperature Range. 0°C to +70°C

# Standard Conditions (unless otherwise noted)

Vcc = +5 Volts ±0.5 Volts  $V_{DD} = -12$  Volts ±1.0 Volts,  $V_{DD} = GND$ (Vcc = Substrate Voltage) Operating Temperature (TA)= 0°C to +70°C

14-8

substantial savings in both the coding charge and turn-around time if punched cards were used. Upon receipt of the punched cards or the Truth Table, General Instrument will prepare a computer-generated Truth Table which will be returned to the

NOTE 1: Card and Truth Table format available upon request.

# Chip Enable (CE)

-requires one package in to control the data bits (B1-B10) and, if required, the Data Ready and Any Key Output, Any Key Output (AKO) -requires one package pin to indicate a key depression. Output Data Bit 10 (B10) -requires one package pin when ten data bits are required to encode each key,

Select the pin options desired: External Clock + 4 of the following functions

Internal Oscillator + 2 of the following functions LO/RO, CC, CE, AKO, BIO

> \*Exceeding these ratings could cause permanent damage. Functional operation of this device at these conditions is not

implied-operating ranges are specified

beigw.

## ELECTRICAL CHARACTERISTICS

| Characteristics                                               | Sym                                     | Min            | Тур** | Мах     | Units    | Conditions                                                   |

|---------------------------------------------------------------|-----------------------------------------|----------------|-------|---------|----------|--------------------------------------------------------------|

| Clock Frequency                                               | f                                       | 10             | 50    | 100     | КНz      | See Block diagram footnote*<br>for typical R-C values        |

| External Clock Width                                          |                                         | 7              | -     | - 1     | μs       |                                                              |

| Deta & Clock Input<br>(Shift, Control,<br>Complement Control, |                                         |                |       |         |          |                                                              |

| Lockout/Rotlover,<br>Chip Enable                              |                                         |                |       |         |          |                                                              |

| & External Clock)                                             |                                         |                |       | +0,6    | l v      |                                                              |

| Logic "0" Level                                               | V16                                     | Vac<br>Vcc=1.5 | _     | Vcc+0.3 | v        |                                                              |

| Logic "1" Level<br>Shift & Control Input                      | Vti                                     | Vcc-1.5        | 95    | 120     | μА       | V₁ ≈ +5V                                                     |

| Current                                                       | Jase                                    | /5             | 95    | 120     | μΑ       | V1 ~ TOV                                                     |

| Coutput (X <sub>0</sub> -X <sub>8</sub> )                     | ĺ.                                      |                | 170   | 400     |          | Vovr = Vcc (See Note 2)                                      |

| Lagic "1" Output Current                                      | l si                                    | 40             | 170   | 400     | μΑ<br>μΑ | $V_{007} = V_{cc} (See Note 2)$<br>$V_{017} = V_{cc} = 1.3V$ |

|                                                               | 1                                       | 600            | 1300  |         |          | Voir = Vcc-2.0V                                              |

|                                                               |                                         | 900            | 1600  | 3500    | μA       |                                                              |

|                                                               | 1                                       | 1500           | 3600  | 6000    | Aبر      | $V_{OUT} = V_{CC} = 5V$                                      |

|                                                               | 1.                                      | 3000           | 6000  | 10000   | μA       | Vour = Vcc-10V                                               |

| Logic "0" Output Current                                      | 1x0                                     | B              | 15    | 50      | μA       | Vour Vcc                                                     |

|                                                               | 1                                       | 6              | 11    | 35      | μA       | $V_{out} = V_{cc} - 1.3V$                                    |

|                                                               |                                         | 5              | 10    | 30      | μA       | Vour = Vcc-2.0V                                              |

|                                                               | 1                                       | 2              | 5     | 15      | μA       | Vour ≈ Vcc~5V                                                |

|                                                               | 1                                       | -              | 0.5   | 5       | μA       | V <sub>pur</sub> ≈ V <sub>cc</sub> -10V                      |

| Y Input (Yo"Ye)                                               |                                         |                |       |         |          |                                                              |

| Trip Level                                                    | V <sub>Y</sub>                          | Vec-5          | Vcc~3 | Vcc~2   | v        | Y Input Going Positive (See Note 2)                          |

| Hysterasis                                                    | $\Delta V_{Y}$                          | 0.5            | 0,9   | 1.4     | v        | (See Note 1)                                                 |

| Selected Y Input Current                                      | Jys                                     | 18             | 36    | 100     | μA       | $V_{IN} = V_{CC}$                                            |

|                                                               | 1.13                                    | 14             | 28    | 90      | μA       | $V_{1N} = V_{CC} - 1.3V$                                     |

|                                                               |                                         | 13             | 25    | 80      | νA       | $V_{IN} = V_{CC} - 2.0V$                                     |

|                                                               |                                         | 6              | 12    | 60      | μA       | $V_{iN} = V_{cc} - 5V$                                       |

|                                                               | 1                                       |                | 1     | 30      | μA       | $V_{IN} = V_{CC} - 10V$                                      |

| Unselected Y input Current                                    | lye                                     | 9              | 18    | 50      | μA       | $V_{IN} = V_{CC}$                                            |

| onselected / input ourrent                                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 7              | 14    | 45      | μA       | $V_{IN} = V_{CC} - 1.3V$                                     |

|                                                               | 1                                       | 6              | 13    | 40      | шA       | $V_{\rm IN} = V_{\rm CC} - 2.0V$                             |

|                                                               |                                         | 3              | 6     | 30      | μA       | $V_{1N} \approx V_{CC} = 5V$                                 |

|                                                               |                                         | 5              | 0.5   | 15      | uА       | $V_{1N} = V_{CC} - 10V$                                      |

|                                                               |                                         | -              |       | 10      | DF       |                                                              |

| input Capacitance                                             | Cin                                     |                | 3     | 1 10    | pr       | at DV (All Inputs)                                           |

| X-Y Precharge                                                 | 1                                       | 1              | 1     | 1       | l .      |                                                              |

| Characteristics                                               | φP                                      | 1500           | 3500  | 5000 -  | μA       | $V = V_{CC}$                                                 |

|                                                               | 1                                       | 200            | 600   | 1500    | μA       | V = Vcc-5 (See Note 2)                                       |

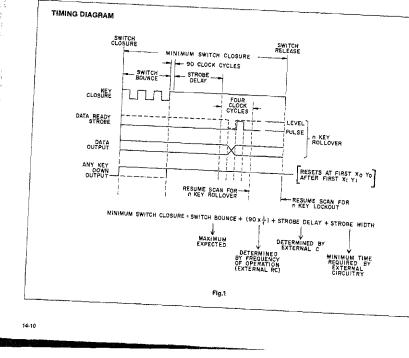

| Switch Characteristics                                        | 1                                       | ł              |       | 1       |          |                                                              |

| Minimum Switch Closure                                        | - 1                                     | -              |       |         | -        | See Timing Diagram                                           |

| Contact Closure                                               | 1                                       | J              | l     | 1       |          | ]                                                            |

| Resistance                                                    | Zcc                                     | - 1            |       | 300     | Ω        |                                                              |

|                                                               | Zco                                     | 1 × 10'        |       | ~~      | Ω        |                                                              |

| Strobe Delay                                                  | 1                                       |                | (     | 1       | Í        |                                                              |

| Trip Level (Pin 31)                                           | Vsn                                     | Vcc-4          | Vcc-3 | Vcc-2   | v        |                                                              |

| Hysteresis                                                    | Vip                                     | 0.5            | 0.9   | 1.4     | v        | (See Note 1)                                                 |

| Quiescent Voltage (Pin 31)                                    | 1 30                                    | -3             | 5     | ~-9     | v        | With Internal Switched Resistor                              |

|                                                               | 1                                       |                |       | 1 °     |          | the second second second                                     |

| Data Output (81-810),<br>Any Key Down Output,                 |                                         |                |       |         |          |                                                              |

| Date Ready                                                    | 1                                       |                |       |         | v        | I <sub>01</sub> = 1.6m A                                     |

| Logic "0"                                                     |                                         |                | -     | 0.4     |          |                                                              |

| Logic "1"                                                     |                                         | Vec-1          |       | 1 - 1   | V        | $I_{OH} = 1.0m A$                                            |

|                                                               | _                                       | Vce-2          | - 1   | -       | ۷        | l <sub>он</sub> ⇔ 2.2m A                                     |

| Power                                                         | l                                       | 1              |       |         |          |                                                              |

| lee                                                           | - 1                                     | -              | 8     | 12      | mA       | $V_{cc} = +5V$                                               |

|                                                               |                                         |                | в     | 12      | mA       | $V_{og} = -12V$                                              |

\*\*Typical values are at +25°C and nominal voltages.

NOTE

I. Hysteresis is defined as the amount of return required to unlatch an input. 2. Precharge of X outputs and Y inputs occurs during each scanned clock cycle.

14-9

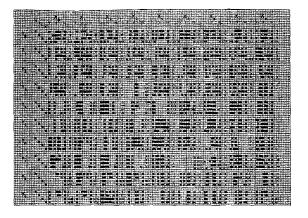

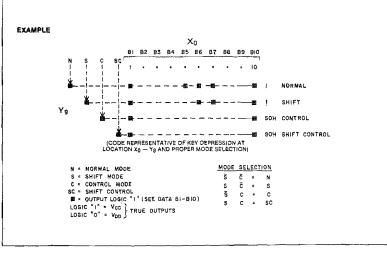

The AY-5-3600 contains (see Block Diagram), a 3600 bit ROM, 9-stage and 10-stage ring counters, a 10 bit comparator, timing circuitry, a 80 bit memory to store the location of encoded keys for n key rollover operation, an externally controllable delay network for eliminating the effect of contact bounce, an output data buffer, and TTL/DTL/MOS compatible output drivers. The ROM portion of the chip is a 360 by 10 bit memory arrangeo

into four 90-word by 10-bit groups. The appropriate levels on the Shift and Control Inputs selects one of the four 90-word groups; the 90-individual word locations are addressed by the two ring counters. Thus, the ROM address is formed by combining the Shift and Control Inputs with the two ring counters, The external outputs of the 9-stage ring counter and the external

inputs to the 10-bit comparator are wired to the keyboard to form an X-Y matrix with the 90-keyboard switches as the crosspoints. In the standby condition, when no key is depressed, the two ring counters are clocked and sequentially address the ROM, thereby scanning the key switches for key closures.

When a key is depressed, a single path is completed between one output of the 9-stage ring counter (X0 thru X8) and one input of the 10-bit comparator  $(Y_0-Y_0)$ . After a number of clock cycles, a condition will occur where a level on the selected path to the comparator matches a level on the corresponding comparator input from the 10-stage ring counter. N KEY ROLLOVER

- When a match occurs, and the key has not been encoded, the switch bounce delay network is enabled. If the key is still de-

pressed at the end of the selected delay time, the code for the pressed at the end or the selected delay limb, the could for the data depressed key is transferred to the output data buffer, the data depressed key is transiened to the output data durier, the data ready signal appears, a one is stored in the encoded key memory and the scan acquence is resumed. If a match occurs at another and the scale acquerice is repeated thus encoding the next key location, the sequence is repeated that showing the text key. If the match occurs for an already encoded key, the match is not recognized. The code of the last key encoded remains in the

# N KEY LOCKOUT

- When a match occurs, the delay network is enabled. If the key is still depressed at the end of the selected delay time, the code for the depressed key is transferred to the output data buffer, the data ready signal appears and the ramaining keys are locked out by halting the scan sequence. The scan sequence is resumed upon key release. The output data buffer stores the code of the

# SPECIAL PATTERNS

- Since the selected coding of each key and all the options are defined during the manufacture of the chip, the coding and options can be changed to fit any particular application of the keyboard. Up to 380 codes of up to 10 bits can be programmed into the AY-5-3600 ROM covering most popular codes such as ASCII, EBCDIC, Selectric, etc., as well as many specialized codes. The ASCII code in conjunction with internal oscillator, 10 data outputs and any key down output, is available as a standard pattern (See Figure 2).

#### FIG.2 CONFIGURATION & CODE OF STANDARD ENCODER

#### **OPTIONS PROVIDED WITH STANDARD ENCODER**

Any Key Output True (Logic 1) During Key Depression.

Device Marking: AY-5-3600

Output Data Bit B1D on Pin No. 5.

Internal Oscillator on Pin Nos. 1, 2, 3. Any Key Output on Pin No. 4.

- N-Key Rollover Only.

- True Outputs Only.

- # Pulse Data Ready Signal.

- Internal Resistor to V<sub>DD</sub> on Shift/Control Pin.

- Plastic Package.

14-11

GI

# AY-5-3600-PRO

# Keyboard Encoder and PROM/EPROM Application

The AY-5-3600-PRO is pre-programmed during manufacture to provide specific yet simple binary coded outputs thus ellowing the purchase of off-the-shelf devices (distributors, etc.). To enhance the device fiexbillity, the binary outputs have been organized to provide direct interface with a PROM/EPROM.

The PROM (Programmable Read Only Memory) permits the programming of the required output code in the factory or tha field within minutes, thus making it extramely suitable for small quantity, fast turnaround keyboard requirements. The EPROM (Erasable Programmable Reed Only Memory) is loteally suited for prototyping, where patterns are quite variable, allowing the EPROM to be erased and reprogrammad repastedly. Similar advantages are realized in the field where pattern changes are necessary in order to respond to redefined requirements or to subtle system peculiarities not previously encountered.

#### **Technical Description**

The AY-5-3600-PRO is a binary coded MOS-LSI device programmed to furnish 360 unique 9-bit codes (90 keys × 4 modes × 9 bits). Option selections include such popular functions as Internal Osciliator, Lockout/Rollover and an Any Key Down output. For further, more explicit device characteristics refer to the preceding pages. The Internal oscillator is a self contained (on-chip) circuit option which eliminates the need for any external clock source. For applications necessitating an external clock source the internal oscillator input pins may be utilized to function in the slave mode of operation. Lockout or Rollover is selectable via an input pin, thus allowing the versatility required on various keyboard applications. The Any Key Down output performs the function of a gating signal by acknowledging both a key depression and release, making it a convanient signal for use in a repeat application.

For ease of translation, each key is assigned an X-Y coordinate and, in turn, each X-Y coordinate has been identified with a specific yet simple binary coded output. Two formets are described: the first for application with a 64 key 4 mode keyboard and the second for a 90 key 4 mode keyboard.

The 64 key 4 mode application as litustrated in Fig. 8 utilized keyboard encoder addresses X0 Y0 thru X6 Y3. A unique combination of one input (Y) and one output (X) is assigned to each key. for a total coverage of 64 keys. Binary coded outputs B2-B6 have been arranged to provide the necessary 8-bit address inputs to the PROM/EPROM, with B2 and B3 representing the variable mode identification and 64-B9 each specific key closure.

When a key is depressed a path is completed between on X line and one Y line thus addressing that specific X-Y ROM coordinate in the AY-5-300-PRO. The 8-bit binary code for that X-Y location (ref. Truth Tabla page 14-15) is transferred into a one character 6bit output latch (82-B9) thus providing the appropriate 8-bit address to the 256x8 PROM/EFROM.

Expansion to a 90 key 4 mode operation (see Fig. 9) is identical to the 84 key 4 mode except: the 90 key 4 mode version utilizes the full complement of addresses X0 Y0 thru X8 Y8 (90 keys). The 8bit binary code (82-89) previously produced to address the 256×8 PROM/EPROM is now expended to a 9-bit binary code (81-89) for addressing to a 512×8 PROM/EPROM. With expansion to a 90 key 4 mode application outputs B1-B3 now serve as the variable mode identification.

The interface to a PROM/EPROM enables the custom programming of the required output date in the PROM/EPROM to directly coincide to the specific address inputs from the AY-5-5600-PRO. Any PROM whether it be bipolar, ultraviolet erasable or electrically alterable, may be employed to provide a wide variety of "off-the-shelt" keyboards. Once the keyboard essembly has gone beyond the prototyping stage, and assuming the quantity/cost permit. the PROM/EPROM deta can be converted to the standard AY-5-3600 data format (ref. AY-5-3600 Custom Coding Information sheet) and produced in production quantities. This eliminates the PROM/EPROM expense while assuring the absence of undefined coding changes.

# Summary of Important Features

- Ability to deliver complete keyboard assemblies within days without ascrificing the features offered in the AY-5-3600 Keyboard Encoder.

- Ability to buy off-the-shelf devices (distributor, etc.)

Ability to verify the specific pattern format using a PROM/

- EPROM prior to a 'custom' encoder commitment.

14-12

14-13

14